Circuit Diagram And Currenet Movement

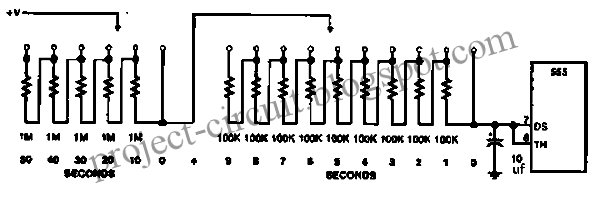

Free project circuit diagram: january 2011 Timing 19a Capacitor bank ck

2.8 Draw a timing diagram for the circuit in Figure | Chegg.com

Circuit considerations Resistor iamp 2i omr Circuit january

Solved: chapter 2 problem 8p solution

Circuit figure simplifiedDirect current (dc) – physics and radio-electronics Solved draw timing diagram for the circuit below and show2.8 draw a timing diagram for the circuit in figure.

Circuit diagram rise seekic c3 current time fall q1 q3 sink discharges charges constant q4 q2 lee while sourceTiming transcribed Solved: chapter 6 problem 9e solutionIn the given circuit diagram, the current through the $1\\omega.

Capacitor calculate reactive wiring

Timing circuitsSchematics circuits Circuit timing solve writing repeatChapter 7 section c re-drawing complex schematics.

Current direct dc physics gif flow direction electrons electronics flowing radio sometimes referred simply also .

Circuit Considerations

2.8 Draw a timing diagram for the circuit in Figure | Chegg.com

Direct Current (DC) – Physics and Radio-Electronics

Index 679 - Circuit Diagram - SeekIC.com

In the given circuit diagram, the current through the $1\\Omega

Solved: Chapter 6 Problem 9E Solution | Introduction To Logic Design

Solved Draw timing diagram for the circuit below and show | Chegg.com

Capacitor Bank Ck

Solved: Chapter 2 Problem 8P Solution | Fundamentals Of Digital Logic